Republic of Iraq Ministry of Higher Education & Scientific Research Northern Technical University Technical College of Kirkuk Electronic & Control Dept.

# Digital Electronics

# **1-Number Systems**

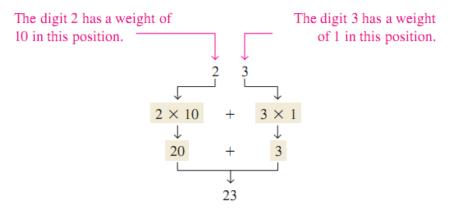

#### **1.1 Decimal Numbers**

You are familiar with the decimal number system because you use decimal numbers every day. Although decimal numbers are commonplace, their weighted structure is often not understood. The decimal number system has ten digits. Each of the ten digits, 0 through 9, represents a certain quantity

#### **1.2 Binary Number**

The binary number system is another way to represent quantities. It is less complicated than the decimal system because it has only two digits. The decimal system with its ten digits is a base-ten system; the binary system with its two digits is a base-two system. The two binary digits (bits) are 1 and 0. The weights in a binary number are based on powers of two.

| Table 1        |   |         |      |    |

|----------------|---|---------|------|----|

| Decimal Number | В | inary 1 | Numb | er |

| 0              | 0 | 0       | 0    | 0  |

| 1              | 0 | 0       | 0    | 1  |

| 2              | 0 | 0       | 1    | 0  |

| 3              | 0 | 0       | 1    | 1  |

| 4              | 0 | 1       | 0    | 0  |

| 5              | 0 | 1       | 0    | 1  |

| 6              | 0 | 1       | 1    | 0  |

| 7              | 0 | 1       | 1    | 1  |

| 8              | 1 | 0       | 0    | 0  |

| 9              | 1 | 0       | 0    | 1  |

| 10             | 1 | 0       | 1    | 0  |

| 11             | 1 | 0       | 1    | 1  |

| 12             | 1 | 1       | 0    | 0  |

| 13             | 1 | 1       | 0    | 1  |

| 14             | 1 | 1       | 1    | 0  |

| 15             | 1 | 1       | 1    | 1  |

As you have seen in Table1, four bits are required to count from zero to 15. In general, with n bits you can count up to a number equal to  $2^{n} - 1$ . The weight or value of a bit increases from right to left in a binary number.

## 1.2.1 Binary-to-Decimal Conversion

The decimal value of any binary number can be found by adding the weights of all bits that are 1 and discarding the weights of all bits that are 0.

Example: Convert the binary number 1101101 to decimal. Solution

weight:  $2^{6}$   $2^{5}$   $2^{4}$   $2^{3}$   $2^{2}$   $2^{1}$   $2^{0}$ binary number:1 1 0 1 1 0 1

$1101101 = 2^{6} + 2^{5} + 2^{4} + 2^{3} + 2^{2} + 2^{1} + 2^{0}$

ement = 64 + 32 + 8 + 4 + 1 = 109

Example:

Convert the fractional binary number 0.1011 to decimal. Solution

weight:  $2^{-1}$   $2^{-2}$   $2^{-3}$   $2^{-4}$ *binary number*:0. 1 0 1 1  $0.1011 = 2^{-1} 2^{-3} 2^{-4}$ = 0.5 + 0.125 + 0.0625 = 0.6875

## 1.2.2 Decimal-to-Binary Conversion

1- Sum-of-Weights Method

To get the binary number for a given decimal number, find the binary weights that adds up to the decimal number.

Example: Convert the following decimal numbers to binary: (a) 12 (b) 25 (c) 58 (d) 82 Solution  $12 = 8 + 4 = 2^3 + 2^2 \rightarrow 1100$ *a*)  $25 = 16 + 8 + 1 = 2^4 + 2^3 + 2^0 \rightarrow 11001$ *b*)  $58 = 32 + 16 + 8 + 2 = 2^5 + 2^4 + 2^3 + 2^1 \rightarrow 111010$ c)

$82 = 64 + 16 + 2 = 2^6 + 2^4 + 2^1 \rightarrow 1010010$ d)

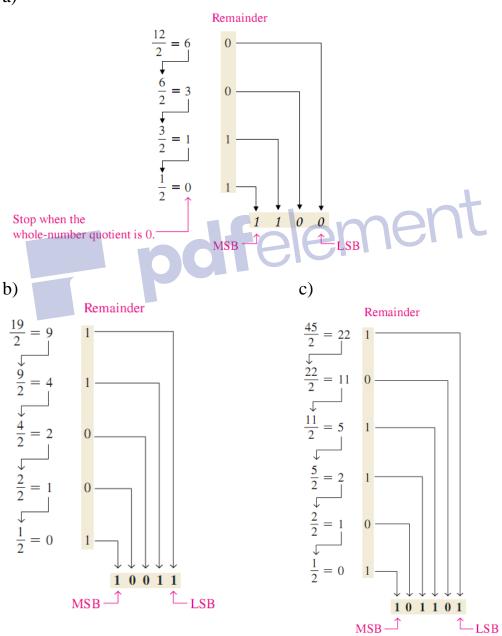

## 2- Repeated Division-by-2 Method

To get the binary number for a given decimal number, divide the decimal number by 2 until the quotient is 0. Remainders form the binary number.

Example: Convert the following decimal numbers to binary: a) 12 b) 19 c) 45

#### Solution

a)

MSB: Most Significant Bit. LSB: Least Significant Bit

## **1.2.3 Converting Decimal Fractions to Binary**

1- Sum-of-Weights

The sum-of-weights method can be applied to fractional decimal numbers, as shown in the following example:  $0.625 = 0.5 + 0.125 = 2^{-1} + 2^{-3} = 0.101$

There is a 1 in the  $2^{-1}$  position, a 0 in the  $2^{-2}$  position, and a 1 in the  $2^{-3}$  position.

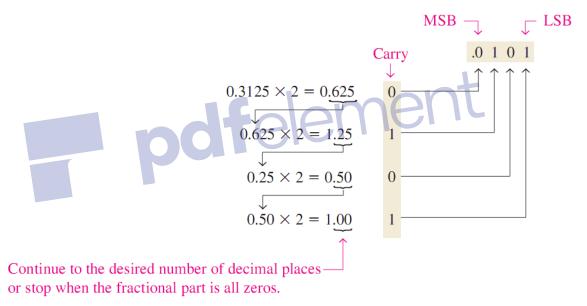

2- Repeated Multiplication by 2

Decimal fractions can be converted to binary by repeated multiplication by 2.

Example

Convert the decimal fraction 0.3125 to binary.

#### **H.W**

- Convert each decimal number to binary by using the sum-of-weights method:

(a) 23 (b) 57 (c) 45.5

- 2. Convert each decimal number to binary by using the repeated division-by-2 method (repeated multiplication-by-2 for fractions):

- (a) 14 (b) 21 (c) 0.375

## 1.2.4 Binary Arithmetic

Binary arithmetic is essential in all digital computers and in many other types of digital systems. To understand digital systems, you must know the basics of binary addition, subtraction, multiplication, and division.

#### 1- Binary Addition

The four basic rules for adding binary digits (bits) are as follows:

| 0 | + | 0 | = 0 | Sum of 0 with carry of 0 |

|---|---|---|-----|--------------------------|

| 0 | + | 1 | =1  | Sum of 1 with carry of 0 |

| 1 | + | 0 | =1  | Sum of 1 with carry of 0 |

| 1 | + | 1 | =10 | Sum of 0 with carry of 1 |

When there is a carry of 1, you have a situation in which three bits are being added (a bit in each of the two numbers and a carry bit). This situation is illustrated as follows:

carry

bits  $\downarrow$  1 + 0 + 0 = 01 Sum of 1 with carry of 0 1 + 1 + 0 = 10 Sum of 0 with carry of 1 1 + 0 + 1 = 10 Sum of 1 with carry of 1 1 + 1 + 1 = 11 Sum of 1 with carry of 1

Example

Add the following binary numbers: (a) 11 + 11 (b) 100 + 10 (c) 111 + 11 (d) 110 + 100

Solution

The equivalent decimal addition is also shown for reference.

| <i>a</i> ) | 11  | 3  | <i>b</i> ) | 100 | 4  | <i>c</i> ) | 111  | 7  | <i>d</i> ) | 110  | 6  |

|------------|-----|----|------------|-----|----|------------|------|----|------------|------|----|

|            | +11 | +3 |            | +10 | +2 |            | +11  | +3 |            | +100 | +4 |

|            | 110 | 6  |            | 110 | 6  |            | 1010 | 10 |            | 1010 | 10 |

SECOND YEAR

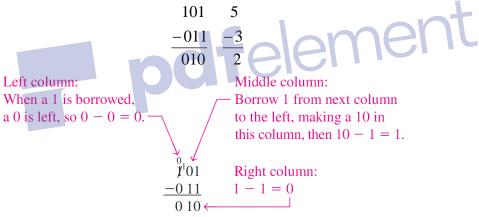

2- Binary Subtraction

The four basic rules for subtracting bits are as follows:

#### Example

Perform the following binary subtractions: (a)  $11 \quad 01 \quad (b) \quad 11 \quad 10$

| (a)        | 11-(  | JI | (D) 11     | -10 |   |

|------------|-------|----|------------|-----|---|

| Solu       | ution |    |            |     |   |

| <i>a</i> ) | 11    | 3  | <i>b</i> ) | 11  | 3 |

|            | _01   | 1  |            | _10 | C |

| -01 | -1 | -10 | -2 |

|-----|----|-----|----|

| 10  | 2  | 01  | 1  |

Example Subtract 011 from 101. Solution

#### **)** H.W

- 1- Perform the following binary subtractions.

- a) 111 100.

- b) 110-001

- 2- Subtract 101 from 110.

**SY**

#### 3- Binary Multiplication

The four basic rules for multiplying bits are as follows:

$0 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 0 = 0$  $1 \times 1 = 1$

#### Example

Perform the following binary multiplications:

| (a)        | 11 ×  | 11         | (b)        | 101        | ×   | 111        |

|------------|-------|------------|------------|------------|-----|------------|

| Sol        | ution |            |            |            |     |            |

| <i>a</i> ) | 11    | 3          | <i>b</i> ) | 1          | 11  | 7          |

|            | ×11   | $\times 3$ |            | ×1(        | )1  | $\times 5$ |

|            | 11    | 9          |            | 1          | 11  | 35         |

|            | +110  |            |            | 00<br>+111 |     |            |

|            | 1001  |            | -          | 1000       | )11 |            |

4- Binary Division

Division in binary follows the same procedure as division in decimal.

Example

| Perform the fo                                                                                                              | ollowing binar                               | ry divisions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) 110÷11                                                                                                                  | (b) 110÷10                                   | (c) $1001 \div 11$ (d) $10100 \div 100$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Solution                                                                                                                    |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| a) $11)110$                                                                                                                 | b) $10)110$                                  | $2\overline{)6}$ c) $11\overline{)1001}$ $3\overline{)9}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\frac{-110}{000}$                                                                                                          |                                              | $ \frac{-6}{0} \qquad \frac{-11}{011} \qquad \frac{-9}{0} \\ \underline{-11} \qquad 2 \qquad -11 \qquad -1$ |

| $\begin{array}{c} 101\\ d) & 100 \overline{\smash{\big)}10100}\\ -100\\ \hline 00100\\ -100\\ \hline 00\\ 00\\ \end{array}$ | $00$ $4\overline{\smash{\big)}20}$ $-20$ $0$ | <ul> <li>نأخذ الاعداد من اليسار.</li> <li>في حالة ناتج الطرح ليس صفر العدد أصغر يضاف صفر الى الناتج ثم يتم إنزال العدد الذي يليه</li> <li>في حالة بقاء اصفار فقط وناتج الطرح اصفار فقط يتم وضعها مباشرة في الناتج</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **H.W**

1. Perform the following binary additions:

a) 1101+1010 (b) 10111+01101

2. Perform the following binary subtractions:

a) 1101–0100 (b) 1001–0111

- 3. Perform the indicated binary operations:

- a)  $110 \times 111$  (b)  $1100 \div 011$  (c)  $1101 \times 1010$  (d)  $1111 \div 101$

# 1.2.5 Signed Binary Numbers

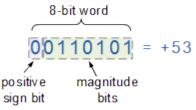

Positive Signed Binary Numbers

Negative Signed Binary Numbers

unsigned numbers can have a wide range of representation. But whereas, in case of signed numbers, we can represent their range only from

$-(2^{n-1}-1)to + (2^{n-1}-1)$ Where n is the number of bits (including sign bit).

Example:

For a 5 bit signed binary number (including 4 magnitude bits & 1 sign bit), the range will be

$$-(2^{(5-1)}-1)$$

to  $+(2^{(5-1)}-1)$

$-(2^{(4)}-1)$  to  $+(2^{(4)}-1)$

$-15$  to  $+15$

Unsigned 8- bit binary numbers will have range from 0-255. The 8 – bit signed binary number will have maximum and minimum values as shown below.

The maximum positive number is 0111 1111 +127 The maximum negative number is 1000 0000 -127

There are three common ways to represent negative numbers within the computer. They are

- 1) Signed magnitude representation.

- 2) 1's compliment representation.

- 3) 2's complement representation.

#### 1- Signed magnitude representation

The binary numbers which can be identified by their MSB (Most Significant Bit), whether they are positive or negative are called "Signed binary numbers".

**Ex:**  $1001 \rightarrow +9(positive)$ ,  $1001 \rightarrow -1(negative)$

This is the simplest way of representing the both positive and negative numbers in binary system. In the signed magnitude representation,

- Positive number is represented with '0' at its most significant bit (MSB).

- Negative number is represented with '1' at its most significant bit (MSB).

#### 2- One's Complement of a Signed Binary Number

1's complement is another way of feeding the negative binary number to the computer. In one's complement method, the positive binary numbers are unchanged. But the negative numbers are represented by taking 1's complement of unsigned positive number.

A positive number always starts with 0, at its MSB while a negative number always starts with 1, at its MSB.

## Finding the 1's Complement

The 1's complement of a binary number is found by changing all 1s to 0s and all 0s to 1s, as illustrated below:

|                             | 10110010                                                                                                                   | Binary number               |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|                             | $\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow$ |                             |

|                             | 0 1 0 0 1 1 0 1                                                                                                            | 1's complement              |

| Ex:If a binary number is    | $s 01101001 = (105)_{10},$                                                                                                 |                             |

| then its one's compleme     | ent is 10010110 =(-10                                                                                                      | $(5)_{10}$                  |

| Ex: -33 =?                  |                                                                                                                            |                             |

| 33 is represented as (10    | $(0001)_2$                                                                                                                 |                             |

| In 8 bit notation, it is re | presented as (0010 00                                                                                                      | 01) <sub>2</sub>            |

| Now, -33 is represented     | in one's compliment                                                                                                        | as (1101 1110) <sub>2</sub> |

| Ex : -127 =?                |                                                                                                                            |                             |

| In 8 bit notation, 127 is   | represented as (0111                                                                                                       | 1111)2                      |

| Now, -127 is represente     | d in one's complimen                                                                                                       | t as $(1000\ 0000)_2$       |

| Ex : -1 =?                  |                                                                                                                            |                             |

| 1 is represented as (001)   | 02                                                                                                                         |                             |

| In 8 bit notation, it is re | presented as (0000 00                                                                                                      | 01)2                        |

| Now, -1 is represented i    | n one's compliment a                                                                                                       | s (1111 1110)2              |

|                             |                                                                                                                            |                             |

#### Subtraction using 1's compliment

To subtract a number from another binary number, first it has to be converted into its one's compliment.

There are 3 possible cases for subtracting the negatives numbers by using 1's compliment.

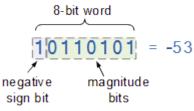

**Case 1** : Negative number smaller than positive number.

**Ex:** (28)<sub>10</sub> & (-15)<sub>10</sub>

We know 28 is represented in binary number system as (011100)<sub>2</sub>

15 is represented in binary number system as  $(01111)_2$

1's compliment of 15 is (10000)<sub>2</sub> i.e. -15

$(13)_{10}$  is same as 0 01101 in binary system.

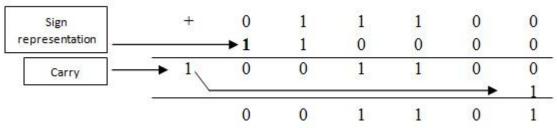

**Case 2:** Negative number greater than positive number. **Ex:**  $(15)_{10}(-28)_{10}$

We know 28 is represented in binary number system as  $(011100)_2$ 15 is represented in binary number system as  $(01111)_2$ 1's compliment of 28 is  $(100011)_2$  i.e. -28

| Sign<br>representation | +             | 1   | 0 | 0 | 0 | 1 | 1 |

|------------------------|---------------|-----|---|---|---|---|---|

|                        |               | → 0 | 0 | 1 | 1 | 1 | 1 |

|                        | 5 <del></del> | 1   | 1 | 0 | 0 | 1 | 0 |

$(-13)_{10}$  is same as 1 10010 in binary system.

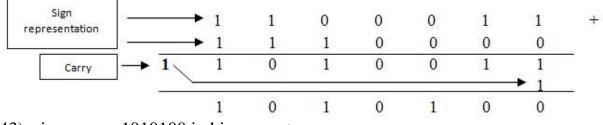

**Case 3:** both are negative.

**Ex:**  $(-28)_{10}$  &  $(-15)_{10}$

We know 28 is represented in binary number system as (011100)<sub>2</sub>

1's compliment of 28 is (100011)2i.e. -28

15 is represented in binary number system as  $(01111)_2$

1's compliment of 15 is  $(10000)_2$  i.e. -15

$(-43)_{10}$  is same as 1010100 in binary system.

## 3- Two's Complement of a Signed Binary Number

Finding the 2's Complement

The 2's complement of a binary number is found by adding 1 to the LSB of the 1's complement.

2's complement = (1's complement) + 1

Ex Find the 2's complement of 10110010.

| 10110010 | Binary number  |

|----------|----------------|

| 01001101 | 1's complement |

| + 1      | Add 1          |

| 01001110 | 2's complement |

**Ex:** -33 =?

33 is represented as  $(100001)_2$

In 8 bit notation, it is represented as  $(0010\ 0001)_2$

Now, -33 is represented in one's compliment as  $(1101 \ 1110)_2$

Adding 1 (0000 0001) to it,

The result is  $(1101 \ 1111)_2$

Therefore, the two's complement of the number -33 is  $(1101 \ 1111)_2$ .

**Ex:** -127 =?

In 8 bit notation, 127 is represented as (0111 1111)<sub>2</sub>

Now, -127 is represented in one's compliment as (1000 0000)<sub>2</sub>

Adding 1 (0000 0001) to it,

The result is (1000 0001)<sub>2</sub>

Therefore, the two's complement of the number -127 is  $(1000\ 0001)_2$

**Ex:** -1 =?

1 is represented as  $(001)_2$

In 8 bit notation, it is represented as (0000 0001)<sub>2</sub>

Now, -1 is represented in one's compliment as  $(1111\ 1110)_2$

Adding 1 (0000 0001) to it,

The result is (0000 0010)<sub>2</sub>

Therefore, the two's complement of the number -1 is  $(0000\ 0010)_2$

2's complement subtraction

For subtracting a <u>smaller number from a larger number</u>, the 2's complement method is as follows:

- 1. Determine the 2's complement of the smaller number.

- 2. Add the 2's complement to the larger number.

- 3. Discard the final carry (there is always one in this case).

#### Example Use 2's complement to subtract the 11001-10011. Solution

| 10011                                                    | smaller number                    |  |

|----------------------------------------------------------|-----------------------------------|--|

| $ \begin{array}{r} 01100 \\ + 1 \end{array} $            | 1's complement<br>Add 1           |  |

| $\overline{\begin{array}{c} 01101\\ +11001 \end{array}}$ | 2's complement<br>larger number   |  |

| $\frac{100110}{000110}$                                  | Discard the final carry<br>result |  |

|                                                          | result                            |  |

For subtracting a larger number from a smaller number, the 2's complement method is as follows:

- 1. Determine the 2's complement of the larger number.

- 2. Add the 2's complement to the smaller number.

- 3. There is no carry from the left-most column. The result is in 2's complement form and is negative.

- 4. Change the sign and take the 2's complement of the result to get the final answer. ement

Example

# Subtract 11100 from 10011 Using 2's complement. Solution

| 11100                                         | larger number                       |

|-----------------------------------------------|-------------------------------------|

| $ \begin{array}{r} 00011 \\ + 1 \end{array} $ | 1's complement<br>Add1              |

| 00100<br>+10011                               | 2's complement<br>smaller number    |

| 10111                                         | first result                        |

| 01000                                         | 1's complement                      |

| $+ 1 \over 01001$                             | Add1<br>result with out sign        |

| - 01001                                       | change sign to get the final answer |

## **1.3 Octal Number**

The octal number system is composed of eight digits, which are 0, 1,2,3,4,5,6,7. To count above 7, begin another column and start over 10, 11, 12.....etc. The octal number system has a base of 8

| Decimal | Octal | Decimal | Octal |

|---------|-------|---------|-------|

| 0       | 0     | 8       | 10    |

| 1       | 1     | 9       | 11    |

| 2       | 2     | 10      | 12    |

| 3       | 3     | 11      | 13    |

| 4       | 4     | 12      | 14    |

| 5       | 5     | 13      | 15    |

| 6       | 6     | 14      | 16    |

| 7       | 7     | 15      | 17    |

# 1.3.1 Octal-to-Decimal Conversion

The conversion of an octal number to its decimal equivalent is accomplished by multiplying each digit by its weight and summing the products, as illustrated here  $for(2374)_8$ .

emer

weight:  $8^3$   $8^2$   $8^1$   $8^0$ binary number: 2 3 7 4  $(2374)_8 = (2 \times 8^3) + (3 \times 8^2) + (7 \times 8^1) + (4 \times 8^0)$   $= (2 \times 512) + (3 \times 64) + (7 \times 8) + (4 \times 1)$  = 1024 + 192 + 56 + 4 $= (1276)_{10}$

**Theorem 1** H.W / Determine the decimal value of  $(0.325)_8$

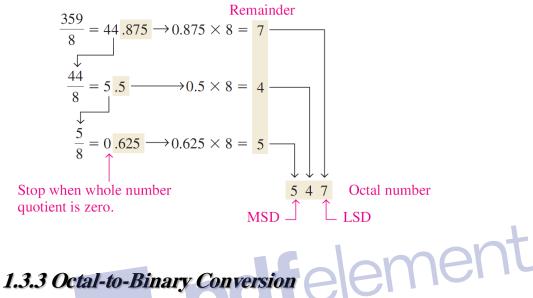

# 1.3.2 Decimal-to-Octal Conversion

A method of converting a decimal number to an octal number is the repeated division-by-8 method.

Example

Convert the following decimal number to octal number 359. Solution

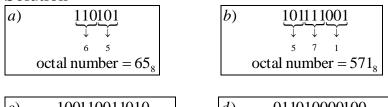

Because each octal digit can be represented by a 3-bit binary number, it is very easy to convert from octal to binary. Each octal digit is represented by three bits as shown in Table 2.

| Table 2                  |     |     |     |     |     |     |     |     |  |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

| Octal/binary conversion. |     |     |     |     |     |     |     |     |  |

| Octal Digit              | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |  |

| Binary                   | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |  |

To convert an octal number to a binary number, simply replace each octal digit with the appropriate three bits.

Example

Convert each of the following octal numbers to binary:

*ler*

# 1.3.4 Binary-to-Octal Conversion

To convert a binary number to an octal number simply break the binary number to groups of three bits and convert each group in to the appropriate octal digit.

Example

Convert each of the following binary numbers to octal: a) 110101 (b) 101111001 (c) 100110011010 (d) 11010000100 Solution

| c) <u>100110011010</u>                                   | <i>d</i> ) <u>011010000100</u>                |

|----------------------------------------------------------|-----------------------------------------------|

| $\downarrow \downarrow \downarrow \downarrow \downarrow$ | $\downarrow \downarrow \downarrow \downarrow$ |

| 4 6 3 2                                                  | 3 2 0 4                                       |

| octal number = $4632_8$                                  | octal number = $3204_8$                       |

## **H.W**

1. Convert the following octal numbers to decimal:

a) 73<sub>8</sub> (b) 125<sub>8</sub>

- 2. Convert the following decimal numbers to octal:

a) 98<sub>10</sub> (b) 163<sub>10</sub>

- 3. Convert the following octal numbers to binary:

a)  $46_8$  (b)  $723_8$  (c)  $5624_8$

- 4. Convert the following binary numbers to octal:

- a) 110101111 (b) 1001100010 (c) 10111111001

## **1.4 Hexadecimal Numbers**

The hexadecimal number system has sixteen characters; it is used primarily as a compact way of displaying or writing binary numbers because it is very easy to convert between binary and hexadecimal.

The hexadecimal number system consists of digits 0–9 and letters A–F. Each hexadecimal digit represents a 4-bit binary number (as listed in Table 3).

| Table 3 |        |             |      |

|---------|--------|-------------|------|

| Decimal | Binary | Hexadecimal |      |

| 0       | 0000   | 0           | ]    |

| 1       | 0001   | 1           |      |

| 2       | 0010   | 2           |      |

| 3       | 0011   | 3           |      |

| 4       | 0100   | 4           |      |

| 5       | 0101   | 5           | ]    |

| 6       | 0110   | б           | ]    |

| 7       | 0111   | 7           |      |

| 8       | 1000   | 8           | ]    |

| 9       | 1001   | 9           |      |

| 10      | 1010   | A           | meri |

| 11      | 1011   | B           |      |

| 12      | 1100   | С           |      |

| 13      | 1101   | D           | ]    |

| 14      | 1110   | Е           |      |

| 15      | 1111   | F           | ]    |

|         |        |             |      |

# 1.4.1 Binary-to-Hexadecimal Conversion

Converting a binary number to hexadecimal is a straightforward procedure. Simply breaks the binary numbers into 4-bit groups, starting at the right-most bit and replace each 4-bit group with the equivalent hexadecimal symbol.

Example

Convert the following binary numbers to hexadecimal:

a) 1100101001010111 (b) 111111000101101001

Solution

| <i>a</i> ) | 1100       | 1100101001010111 |      |        |                   |  |  |  |  |  |  |

|------------|------------|------------------|------|--------|-------------------|--|--|--|--|--|--|

|            | Ý          | Ļ                | Ť    | Ļ      |                   |  |  |  |  |  |  |

|            | С          | Α                | 5    | 7      |                   |  |  |  |  |  |  |

|            | hexadecima | a l ni           | imbe | r = CA | 457 <sub>16</sub> |  |  |  |  |  |  |

| <i>b</i> ) | 00111111000101101001               |   |   |               |              |               |  |  |  |  |

|------------|------------------------------------|---|---|---------------|--------------|---------------|--|--|--|--|

|            |                                    | ¥ | Ť | $\rightarrow$ | $\downarrow$ | $\rightarrow$ |  |  |  |  |

|            |                                    | 3 | F | 1             | 6            | 9             |  |  |  |  |

|            | hexadecima l number = $3F169_{16}$ |   |   |               |              |               |  |  |  |  |

Two zeros have been added in part (b) to complete a 4-bit group at the left.

⇒ H.W/ Convert the binary number 1001111011110011100 to hexadecimal.

E

# 1.4.2 Hexadecimal-to-Binary Conversion

To convert from a hexadecimal number to a binary number, reverse the process and replace each hexadecimal symbol with the appropriate four bits.

Example

Determine the binary numbers for the following hexadecimal numbers:

b)  $CF8E_{16}$ a)  $10A4_{16}$ c)  $9742_{16}$

Solution

a) *b*) 1000010100100 binary number 1100111110001110 *binary number* ==

| <i>c</i> )    |   |              |              |              |              |

|---------------|---|--------------|--------------|--------------|--------------|

|               |   | 9            | 7            | 4            | 2            |

|               |   | $\downarrow$ | $\downarrow$ | $\downarrow$ | $\downarrow$ |

|               |   | $\sim$       | $ \frown $   | $\sim$       | $\sim$       |

| binary number | = | 1001         | 0111         | 0100         | 0010         |

In part (a), the MSB is understood to have three zeros preceding it, thus forming a 4-bit group.

H.W/ Convert the hexadecimal number 6BD3 to binary

# 1.4.3 Hexadecimal-to-Decimal Conversion

One way to find the decimal equivalent of a hexadecimal number is to first convert the hexadecimal number to binary and then convert from binary to decimal.

Example

Convert the following hexadecimal numbers to decimal:

(b)  $A85_{16}$ (a)  $1C_{16}$

Solution

Remember; convert the hexadecimal number to binary first, then to decimal. *a*)

С  $\underbrace{\overset{*}{11100}}_{11100} = 2^4 + 2^3 + 2^2 = 16 + 8 + 4 = 28_{10}$ *binary number* =

*b*)

*binary number* = 101010000101 =  $2^{11} + 2^9 + 2^7 + 2^2 + 2^0 = 2048 + 512 + 128 + 4 + 1 = 2693_{10}$

SECOND YEAR

Or using the sum of weights method

Example

Convert the following hexadecimal numbers to decimal:

(a)  $E5_{16}$  (b)  $B2F8_{16}$

Solution

Recall from Table 3 that letters A through F represent decimal numbers 10 through 15, respectively.

a)  $E5_{16} = (E \times 16^{1}) + (5 \times 16^{0}) = (14 \times 16) + (5 \times 1) = 224 + 5 = 229_{10}$

b)

$$B2F8_{16} = (B \times 16^3) + (2 \times 16^2) + (F \times 16^1) + (8 \times 16^0)$$

=  $(11 \times 4096) + (2 \times 256) + (15 \times 16) + (8 \times 1)$

=  $45056 + 215 + 240 + 8$

=  $45816_{10}$

➡ H.W: Convert the following hexadecimal numbers to decimal.

```

a) 6BD_{16} b) 60A_{16}

```

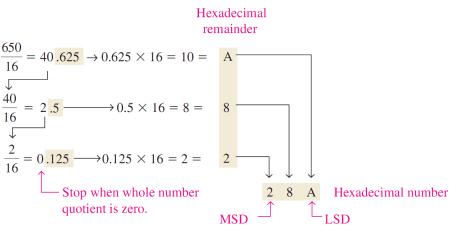

# 1.4.4Decimal-to-Hexadecimal Conversion

Repeated division of a decimal number by 16 will produce the equivalent hexadecimal number, formed by the remainders of the divisions.

Example

Convert the decimal number 650 to hexadecimal by repeated division by 16. Solution

• H.W: Convert decimal 2591 to hexadecimal.

# **1.5 Binary Coded Decimal (BCD)**

Binary coded decimal (BCD) is a way to express each of the decimal digits with a binary code. There are only ten code groups in the BCD system, so it is very easy to convert between decimal and BCD.

# 1.5.1 The 8421 BCD Code

The 8421 code is a type of BCD (binary coded decimal) code. Binary coded decimal means that each decimal digit, 0 through 9, is represented by a binary code of four bits. The designation 8421 indicates the binary weights of the four bits  $2^3$ ,  $2^2$ ,  $2^1$ ,  $2^1$ . The ease of conversion between 8421 code numbers and the familiar decimal numbers is the main advantage of this code. The 8421 code is the predominant BCD code, and when we refer to BCD, we always mean the 8421 code unless otherwise stated.

You should realize that, with four bits, sixteen numbers (0000 through 1111) can be represented but that, in the 8421 code, only ten of these are used. The six code combinations that are not used (1010, 1011, 1100, 1101, 1110, and 1111) are invalid in the 8421 BCD code.

|               |         |       |      | IT ( | ーた   | <b>ブ</b> |      |      |      |      |

|---------------|---------|-------|------|------|------|----------|------|------|------|------|

| Table 4       |         |       |      |      |      |          |      |      |      |      |

| Decimal /BCD  | convers | sion. |      |      |      |          |      |      |      |      |

| decimal Digit | 0       | 1     | 2    | 3    | 4    | 5        | 6    | 7    | 8    | 9    |

| BCD           | 0000    | 0001  | 0010 | 0011 | 0100 | 0101     | 0110 | 0111 | 1000 | 1001 |

To express any decimal number in BCD, simply replace each decimal digit with the appropriate 4-bit code.

Example

Convert each of the following decimal numbers to BCD:

Solution

a)

$$BCD = 00110101$$

b)

$BCD = 10011000$

b)

$BCD = 10011000$

$$\begin{bmatrix} c \\ & 1 & 7 & 0 \\ & \downarrow & \downarrow & \downarrow \\ BCD = & 000101110000 \end{bmatrix} \qquad \begin{bmatrix} d \\ & 2 & 4 & 6 & 9 \\ & \downarrow & \downarrow & \downarrow & \downarrow \\ BCD = & 0010010001101001 \end{bmatrix}$$

H.W: Convert the decimal number 9673 to BCD.

It is equally easy to determine a decimal number from a BCD number. Start at the right-most bit and break the code into groups of four bits. Then write the decimal digit represented by each 4-bit group.

Example

Convert each of the following BCD codes to decimal:

a) 10000110 (b) 00110100001 (c) 1001010001110000

Solution

| $a) \qquad \underbrace{10000110}_{\downarrow}$ | <i>b</i> ) | $\underbrace{001101010001}_{\downarrow}$ | <i>c</i> ) | $\underbrace{1001010001110000}_{\downarrow}$ |

|------------------------------------------------|------------|------------------------------------------|------------|----------------------------------------------|

| decimal number = $86$                          |            | decimal number = $351$                   |            | 9 $4$ $7$ $0decimal number = 9470$           |

H.W: Convert the BCD code 10000010001001110110 to decimal.

# **1.6 BCD Addition**

BCD is a numerical code and can be used in arithmetic operations. Addition is the most important operation because the other three operations (subtraction, multiplication, and division) can be accomplished by the use of addition. Here is how to add two BCD numbers:

- **Step 1-** Add the two BCD numbers, using the rules for binary addition.

- Step 2: If a 4-bit sum is equal to or less than 9, it is a valid BCD number.

- **Step 3:** If a 4-bit sum is greater than 9, or if a carry out of the 4-bit group is generated, it is an invalid result. Add 6 (0110) to the 4-bit sum in order to skip the six invalid states and return the code to 8421. If a carry results when 6 is added, simply add the carry to the next 4-bit group.

Example

Add the following BCD numbers:

a) 0011 + 0100 (b) 00100011 + 00010101 (c) 10000110 + 00010011 (d) 010001010000 + 010000010111

Solution

The decimal number additions are shown for comparison.

| <i>a</i> ) | 0011  | 3  | <i>b</i> ) | 0010  | 0011 | 23  | 1000  | 0110 | 86  |

|------------|-------|----|------------|-------|------|-----|-------|------|-----|

|            | +0100 | +4 |            | +0001 | 0101 | +15 | +0001 | 0011 | +13 |

|            | 0111  | 7  |            | 0011  | 1000 | 38  | 1001  | 1001 | 99  |

| <i>d</i> ) | 0100  | 0101 0000 | 450  |

|------------|-------|-----------|------|

|            | +0100 | 0001 0111 | +417 |

|            | 1000  | 0110 0111 | 867  |

H.W: Add the BCD numbers: 1001000001000011 + 0000100100100101.

Example

Add the following BCD numbers: (a) 1001 + 0100(d) 01100111 + 01010011 Solution

(b) 1001 + 1001 (c) 00010110 + 00010101

#### The decimal number additions are shown for comparison.

| <i>a</i> ) | 1001      |                         |    |

|------------|-----------|-------------------------|----|

|            | +0100     |                         | 9  |

|            | 1101      | Invalid BCD number (>9) | +4 |

|            | +0110     | Add 6                   | 13 |

|            | 0001 0011 | valid BCD number        |    |

| <i>b</i> ) | 1001      |                          |    |

|------------|-----------|--------------------------|----|

|            | +1001     |                          | 9  |

|            | 1 0010    | Invalid because of carry | +9 |

|            | + 0110    | Add 6                    | 18 |

|            | 0001 1000 | valid BCD number         |    |

| <i>c</i> ) | 0001<br>+ 0001 | 0110<br>0101 | 16                                                                                                                 |

|------------|----------------|--------------|--------------------------------------------------------------------------------------------------------------------|

|            | 0010           | 1011 + 0110  | Right group is invalid (> 9), left group is valid. $+15$ Add 6 to invalid code, Add carry 0001 to next group. $31$ |

|            | 0011           | 0001         | valid BCD number                                                                                                   |

|            |                |              |                                                                                                                    |

| <i>d</i> ) | 0110      | 0111  |                                |     |

|------------|-----------|-------|--------------------------------|-----|

|            | + 0101    | 0011  |                                | 67  |

|            | 1011      | 1010  | Both groups are invalid $(>9)$ | +53 |

|            | +0110     | +0110 | Add 6 both groups.             | 120 |

|            | 0001 0010 | 0000  | valid BCD number               |     |

#### **H.W**

- 1- Add the BCD numbers: 01001000 + 00110100.

- 2- Convert the following decimal numbers to BCD: (a

3- What decimal numbers are represented by each BCD code? (a) 10001001 (b) 001001111000 (c) 000101010111

## **1.7 Digital Codes**

# 1.7.1 The Gray Code

The Gray code is unweighted and is not an arithmetic code; that is, there are no specific weights assigned to the bit positions. The important feature of the Gray code is that it exhibits only a single bit change from one code word to the next in sequence. This property is important in many applications, such as shaft position encoders, where error susceptibility increases with the number of bit changes between adjacent numbers in a sequence. Table 5 is a listing of the 4-bit Gray code for decimal numbers 0 through 15. Binary numbers are shown in the table for reference. Like binary numbers, the Gray code can have any number of bits. Notice the single-bit change between successive Gray code words. For instance, in going from decimal 3 to decimal 4, the Gray code changes from 0010 to 0110, while the binary code changes from 0011 to 0100, a change of three bits. The only bit change in the Gray code is in the third bit from the right: the other bits remain the same.

| Table 5 |        |           |

|---------|--------|-----------|

| Decimal | Binary | Gray code |

| 0       | 0000   | 0000      |

| 1       | 0001   | 0001      |

| 2       | 0010   | 0011      |

| 3       | 0011   | 0010      |

| 4       | 0100   | 0110      |

| 5       | 0101   | 0111      |

| 6       | 0110   | 0101      |

| 7       | 0111   | 0100      |

| 8       | 1000   | 1100      |

| 9       | 1001   | 1101      |

| 10      | 1010   | 1111      |

| 11      | 1011   | 1110      |

| 12      | 1100   | 1010      |

| 13      | 1101   | 1011      |

| 14      | 1110   | 1001      |

| 15      | 1111   | 1000      |

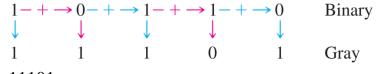

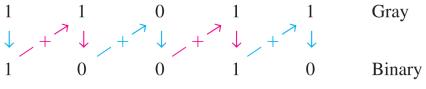

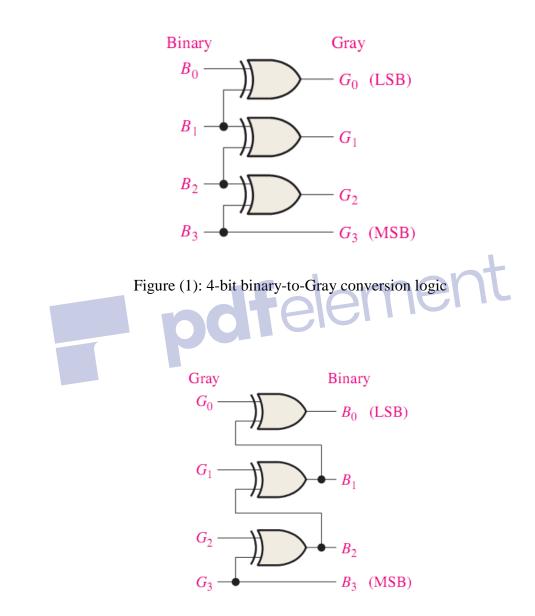

# 1.7.2Binary-to-Gray Code Conversion

Conversion between binary code and Gray code is sometimes useful. The following rules explain how to convert from a binary number to a Gray code word:

- 1. The most significant bit (left-most) in the Gray code is the same as the corresponding MSB in the binary number.

- 2. Going from left to right, add each adjacent pair of binary code bits to get the next Gray code bit. <u>Discard carries.</u>

Example

Convert the following binary number 10110 to Gray code. Solution

The Gray code is 11101.

# 1.7.3Gray-to-Binary Code Conversion

To convert from Gray code to binary, use a similar method; however, there are some differences. The following rules apply:

- 1. The most significant bit (left-most) in the binary code is the same as the corresponding bit in the Gray code.

- 2. Add each binary code bit generated to the Gray code bit in the next adjacent position. <u>Discard carries.</u>

Example

Convert the following Gray code word 11011 to binary. Solution

The binary number is 10010

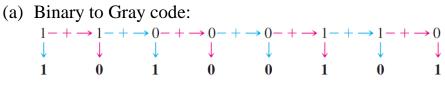

Example

- a) Convert the binary number 11000110 to Gray code.

- b) Convert the Gray code 10101111 to binary

Solution

(b) Gray code to binary:

| 2    |        |       | 2   |      |     |        |     |

|------|--------|-------|-----|------|-----|--------|-----|

| 1    | 0      | 1     | 0   | 1    | 1   | 1      | 1   |

| ↓ _+ | ⊦∕↓ ,⊣ | +~↓_+ | - ^ | + ∕↓ | +~↓ | ⊦ ∕↓ · | +∕↓ |

| 1    | 1      | 0     | 0   | 1    | 0   | 1      | 0   |

**H.W**

- a. Convert binary 101101 to Gray code.

- b. Convert Gray code 100111 to binary.

# 2-Logic Gates

A logic gate is an electronic circuit which makes logic decisions. It has one output and one or more inputs. The output signal appears only for certain combinations of input signals. Logic gates are the basic building blocks from which most of the digital systems.

## 2.1 Types of Logic Gates

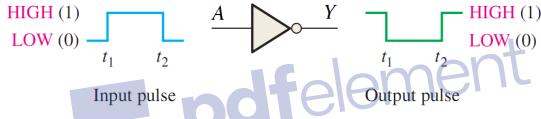

# 1-The NOT Gate (Inverter).

It's so called because its output is NOT the same as its input. It is also called an inverter because it inverts the input signal. This is the simplest form of logic gate and has only 1 input and 1 output. Simply the purpose of this gate is to invert the input signal so if a 0 is at the input, the output will be at 1 and vice versa. The symbol for a NOT gate is as follows.

The output of a logic gate can also be summarised in the form of a table, called a 'Truth Table'. The truth table for a NOT gate is the simplest of all Truth Tables and is shown below.

| Input | Output |

|-------|--------|

| Α     | Y      |

| 0     | 1      |

| 1     | 0      |

The Boolean expression for a NOT gate is

$$Y = \overline{A}$$

The 'bar' over the A indicates that the output Y is the opposite of A.

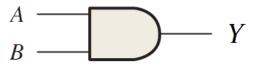

# 2-The AND gate.

The AND gate is one of the basic gates that can be combined to form any logic function. An AND gate can have two or more inputs and performs what is known as logical multiplication. The symbol is:

AND gate produces a 1 output only when all of the inputs are 1. When any of the inputs is 0, the output is 0.

#### **AND Gate Truth Table**

The logical operation of a gate can be expressed with a truth table that lists all input combinations with the corresponding outputs, as illustrated in Table for a 2-input AND gate. The truth table can be expanded to any number of inputs.

$$N=2^{n}$$

Where N is the number of possible input combinations and n is the number of input variables. To illustrate,

For two input variables:  $N = 2^2 = 4$  combinations For three input variables:  $N = 2^3 = 8$  combinations For four input variables:  $N = 2^4 = 16$  combinations

The truth table for the 2 input AND gate is shown below.

| Inp | Output |   |

|-----|--------|---|

| А   | В      | Y |

| 0   | 0      | 0 |

| 0   | 1      | 0 |

| 1   | 0      | 0 |

| 1   | 1      | 1 |

The Boolean expression for a 2 input AND gate is

```

Y = A \cdot B

```

Where: '.' between the A and B means AND in Boolean algebra.

#### The AND gate with 3 inputs.

The symbol is:

$Y = A \cdot B \cdot C$

The truth table for the 3 input AND gate is shown below.

|   | Output |   |   |

|---|--------|---|---|

| А | В      | С | Y |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 0 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 1 |

Example

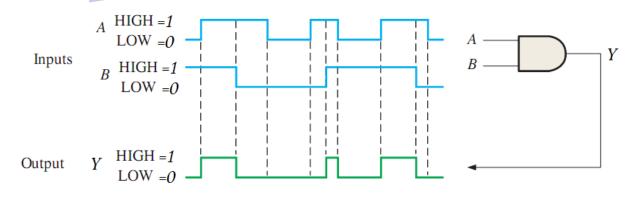

emer If two waveforms, A and B, are applied to the AND gate inputs as in Figure 1, what is the resulting output waveform?

Figure 1

# 3-The OR gate.

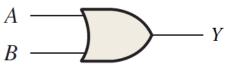

The OR gate is another of the basic gates from which all logic functions are constructed. An OR gate can have two or more inputs and performs what is known as logical addition. The symbol is:

The truth table for the 2 input OR gate is shown below.

| Inp | Output |   |

|-----|--------|---|

| А   | В      | Y |

| 0   | 0      | 0 |

| 0   | 1      | 1 |

| 1   | 0      | 1 |

| 1   | 1      | 1 |

An OR gate produces a 1 on the output when any of the inputs is 1. The output is 0 only when all of the inputs are 0. The Boolean expression for a 2 input OR gate is

Y = A + BWhere: '+' between the A and B means OR in Boolean algebra.

## The OR gate with 3 inputs.

The symbol is:

The truth table for the 3 input OR gate is shown below.

|   | Output |   |   |

|---|--------|---|---|

| А | В      | С | Y |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

Example

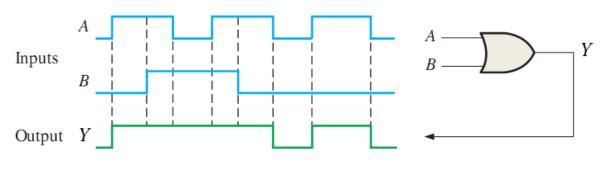

If the two input waveforms, A and B, in Figure2 are applied to the OR gate, what is the resulting output waveform?

Solution

Figure 2

When either or both input waveforms are 1, the output is 1 as shown by the output waveform Y in the timing diagram.

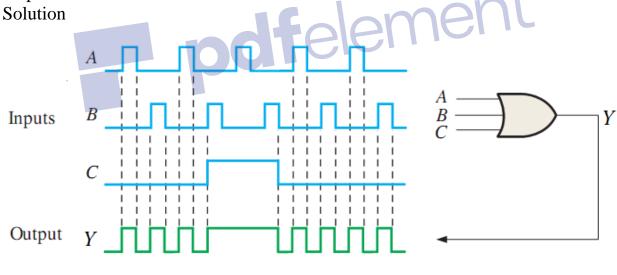

Example

If the 3-input OR gate waveforms, A, B and C, in Figure 3, what is the resulting output waveform?

Figure 3

The output is 1 when one or more of the input waveforms are 1 as indicated by the output waveform Y in the timing diagram.

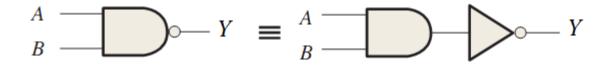

# 4 The NAND gate.

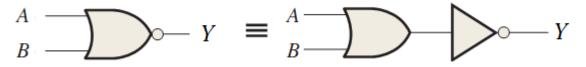

The NAND gate is a popular logic element because it can be used as a universal gate; that is, NAND gates can be used in combination to perform the AND, OR, and inverter operations. The symbol is:

The truth table for the 2 input NAND gate is shown below.

| Inp | Output |   |

|-----|--------|---|

| А   | В      | Y |

| 0   | 0      | 1 |

| 0   | 1      | 1 |

| 1   | 0      | 1 |

| 1   | 1      | 0 |

A NAND gate produces a 0 output only when all the inputs are 1. When any of the inputs is 0, the output will be 1. The Boolean expression for a 2 input NAND gate is

$$Y = A \cdot B$$

Where: '.' between the A and B means AND, and the 'bar' means invert the output in Boolean algebra.

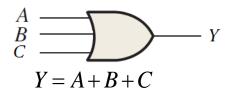

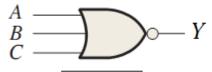

## The NAND gate with 3 inputs.

The symbol is:

$$A = P = \overline{A \cdot B \cdot C}$$

$$Y = \overline{A \cdot B \cdot C}$$

The truth table for the 3 input NAND gate is shown below.

|   | Output |   |   |

|---|--------|---|---|

| А | В      | С | Y |

| 0 | 0      | 0 | 1 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 1 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 0 |

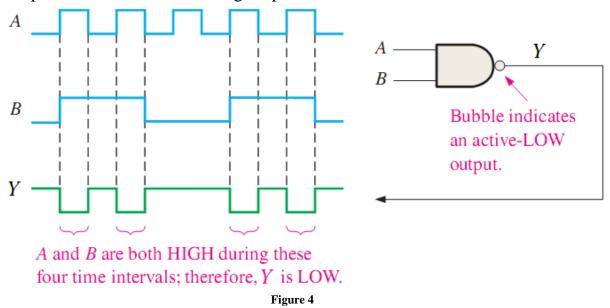

#### Example

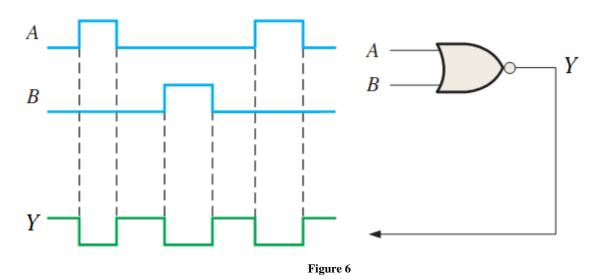

If the two waveforms A and B shown in Figure 4 below are applied to the NAND gate inputs, determine the resulting output waveform.

Output waveform Y is 0 only during the four time intervals when both input waveforms A and B are 1 as shown in the timing diagram.

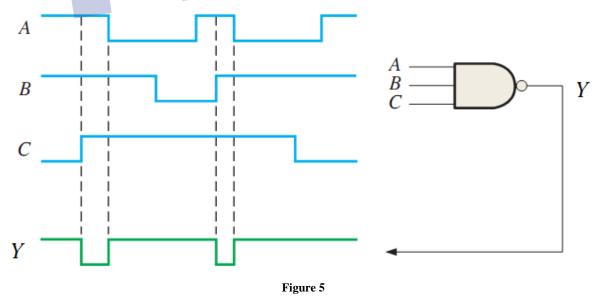

Example

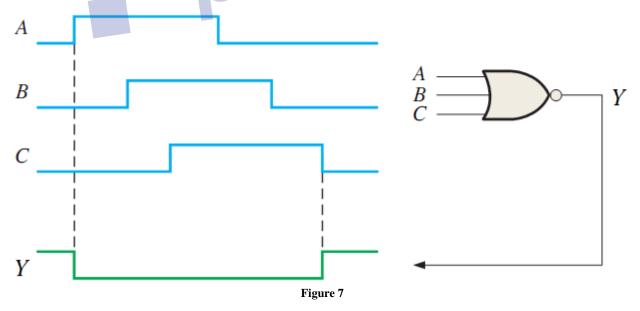

Show the output waveform for the 3-input NAND gate in Figure 5 with its proper time relationship to the inputs.

The output waveform Y is 0 only when all three input waveforms are 1 as shown in the timing diagram.

# 5-The NOR gate.

The NOR gate, like the NAND gate, is a useful logic element because it can also be used as a universal gate; that is, NOR gates can be used in combination to perform the AND, OR, and inverter operations. The symbol is:

The truth table for the 2 input NOR gate is shown below.

| Inputs |   | Output |

|--------|---|--------|

| А      | В | Y      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 0      |

A NOR gate produces a 0 output when any of its inputs is 1. Only when all of its inputs are 0 is the output HIGH. The Boolean expression for a 2 input NOR gate is

Y = A + BWhere: '+' between the A and B means OR and the 'bar' means invert the result in Boolean Algebra.

#### The NOR gate with 3 input.

The symbol is:

$$Y = A + B + C$$

The truth table for the 3 input NOR gate is shown below.

| Inputs |   |   | Output |

|--------|---|---|--------|

| А      | В | С | Y      |

| 0      | 0 | 0 | 1      |

| 0      | 0 | 1 | 0      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 0      |

| 1      | 0 | 0 | 0      |

| 1      | 0 | 1 | 0      |

| 1      | 1 | 0 | 0      |

| 1      | 1 | 1 | 0      |

#### Example

If the two waveforms shown in Figure 3–36 are applied to a NOR gate, what is the resulting output waveform?

Whenever any input of the NOR gate is 1, the output is 0 as shown by the output waveform Y in the timing diagram.

#### Example

Show the output waveform for the 3-input NOR gate in Figure 7 with the proper time relation to the inputs.

The output Y is 0 when any input is 1 as shown by the output waveform Y in the timing diagram.

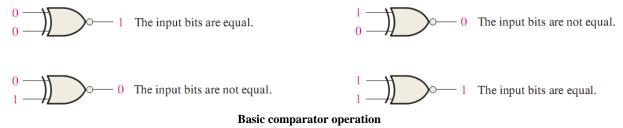

# 6- The XOR gate "Exclusive-OR".

The XOR gate has 2 inputs and is a specialized version of the OR gate. The symbol for a 2 input XOR gate is as follows.

The truth table for the 2 input XOR gate is shown below.

| Inputs |   | Output |

|--------|---|--------|

| А      | В | Y      |

| 0      | 0 | 0      |

| 0      | 1 | 1      |

| 1      | 0 | 1      |

| 1      | 1 | 0      |

For an XOR gate, output Y is 1 when input A is 0 and input B is 1, or when input A is 1 and input B is 0; Y is 0 when A and B are both 1 or both 0. The Boolean expression for a 2 input XOR gate is

$$Y = A \oplus B = AB + AB$$

The ' $\oplus$ ' between the A and B means Exclusive –OR.

## 7- The XNOR gate.

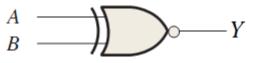

The XNOR gate has 2 inputs and is the inverted form of the EXOR gate. The symbol for a 2 input XNOR gate is as follows.

The truth table for the 2 input XNOR gate is shown below.

| Inputs |   | Output |

|--------|---|--------|

| А      | В | Y      |

| 0      | 0 | 1      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

For an XNOR gate, output Y is 0 when input A is 0 and input B is 1, or when A is 1 and B is 0; Y is 1 when A and B are both 1 or both 0.

The Boolean expression for a 2 input XNOR gate is

$$Y = \overline{A \oplus B} = \overline{AB} + AB$$

The ' $\oplus$ ' between the A and B means Exclusive OR, and the 'bar' means that the result is inverted.

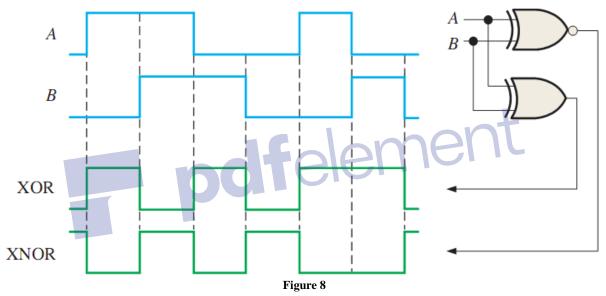

#### Example

Determine the output waveforms for the XOR gate and for the XNOR gate, given the input waveforms, A and B, in Figure 8.

# **3-Boolean Algebra and Combinational Logic**

Boolean algebra is a mathematical system based on logic. It has its own set of fundamental laws which are necessary for manipulating different Boolean expressions:

### **3.1-Basic rules of Boolean algebra.**

| Tab                                                                    | le 6                                                                                                             |          |                                                                                         |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------|

| Basi                                                                   | ic rules of Boolean algebr                                                                                       | ra       |                                                                                         |

| 1                                                                      | $\mathbf{A} + 0 = \mathbf{A}$                                                                                    | 7        | $\mathbf{A} \cdot \mathbf{A} = \mathbf{A}$                                              |

| 2                                                                      | A + 1 = 1 or<br>1+A+B+=1                                                                                         | 8        | $\mathbf{A} \cdot \overline{\mathbf{A}} = 0$                                            |

| 3                                                                      | $\mathbf{A} \cdot 0 = 0$                                                                                         | 9        | $\overline{\overline{\mathbf{A}}} = \mathbf{A}$                                         |

| 4                                                                      | $\mathbf{A} \cdot 1 = \mathbf{A}$                                                                                | 10       | $\mathbf{A} + \mathbf{A}\mathbf{B} = \mathbf{A}$                                        |

| 5                                                                      | $\mathbf{A} + \mathbf{A} = \mathbf{A}$                                                                           | 11       | $\mathbf{A} + \overline{\mathbf{A}}\mathbf{B} = \mathbf{A} + \mathbf{B}$                |

| 6                                                                      | $A + \overline{A} = 1$                                                                                           |          | $\mathbf{A} + \mathbf{B})(\mathbf{A} + \mathbf{C}) = \mathbf{A} + \mathbf{B}\mathbf{C}$ |

| Prov<br>1- A<br>2- (A<br>3- A<br>4- (A<br>5- A<br>Solu<br>4- A<br>AC - | C + ABC = AC $+ ABC = AC(1 + B)$ $= AC$                                                                          | AC       |                                                                                         |

| -                                                                      | (A + B)(A + C) = A + BC<br>$(A + C) = A \cdot A + A \cdot C$<br>= A + A C + C<br>= A (1 + C + C) + C<br>= A + BC | A B + BC |                                                                                         |

$6-A + \overline{A}B = A + B$  $A + \bar{A}B = A \cdot 1 + \bar{A}B$  $= A(1+B) + \bar{A}B$  $= A + AB + \overline{AB}$  $= A + B(A + \overline{A})$ = A + B $7 - (A + B)(A + \overline{B})(\overline{A} + C) = AC$  $(A+B)(A+\overline{B})(\overline{A}+C) = (A \cdot A + A \cdot \overline{B} + A \cdot B + B \cdot \overline{B})(\overline{A}+C)$  $= (A + A\overline{B} + AB + 0)(\overline{A} + C)$  $= A(1 + \overline{B} + B)(\overline{A} + C)$  $= A(1)(\bar{A} + C)$  $= A.\overline{A} + AC$ = AC)  $8-ABC + A\overline{B}C + AB\overline{C} = A(B+C)$  $= AC(B + \overline{B}) + AB\overline{C}$ ement  $= AC + AB\bar{C}$  $= A(C + B\overline{C})$ = A(C + B)= A(B + C)

Example

Simplify the following Boolean expression Y = AB + A(B + C) + B(B + C)Solution

37

Example

Simplify the following Boolean expression: $Y = [A\overline{B}(C + BD) + \overline{A}\overline{B}]C$ Solution

$$Y = [A\overline{B}(C + BD) + \overline{A} \overline{B}]C$$

=  $(A\overline{B}C + A\overline{B}BD + \overline{A} \overline{B})C$

=  $(A\overline{B}C + 0 + \overline{A} \overline{B})C$

=  $A\overline{B}C + \overline{A} \overline{B}C$

=  $\overline{B}C(A + \overline{A})$

$Y = \overline{B}C$

Example

Simplify the following Boolean expression and show the minimum logic gate implementation.  $Y = AB\overline{C} + A\overline{B}\overline{C} + \overline{ABC} + ABC + A\overline{BC}$ Solution  $Y = AB\overline{C} + A\overline{B}\overline{C} + \overline{ABC} + ABC + A\overline{BC}$  $= AB\overline{C} + ABC + A\overline{B}\overline{C} + A\overline{BC} + \overline{ABC}$

$$= ABC + ABC + ABC + ABC + ABC = AB(\bar{C} + C) + A\bar{B}(\bar{C} + C) + \bar{A}BC = A(B + \bar{B}) + \bar{A}BC = A + \bar{A}BC Y = A + BC B C$$

Example

Simplify the following Boolean expression and show the minimum logic gate implementation.  $Y = \overline{AB}\overline{C}\overline{D} + AB\overline{C}\overline{D} + B\overline{C}D$

$$Y = ABCD + ABCD + BCD$$

=  $B\bar{C}\bar{D}(\bar{A} + A) + B\bar{C}D$

=  $B\bar{C}(\bar{D} + D)$

$Y = B\bar{C}$

Example

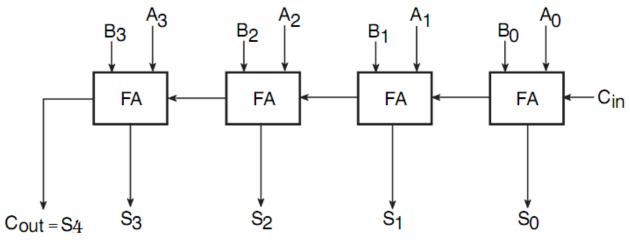

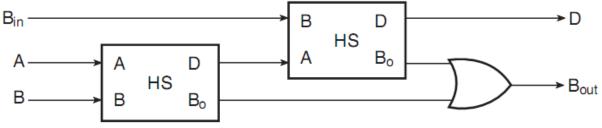

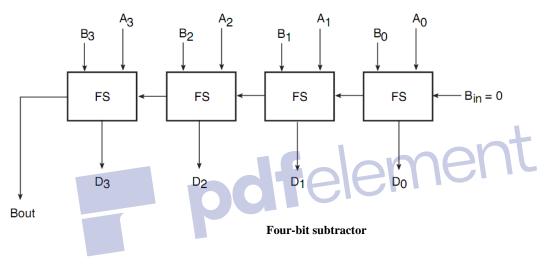

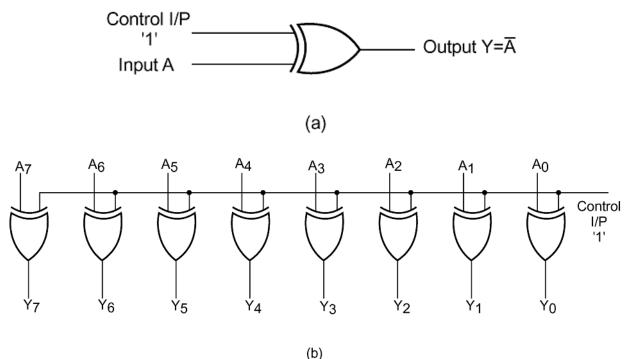

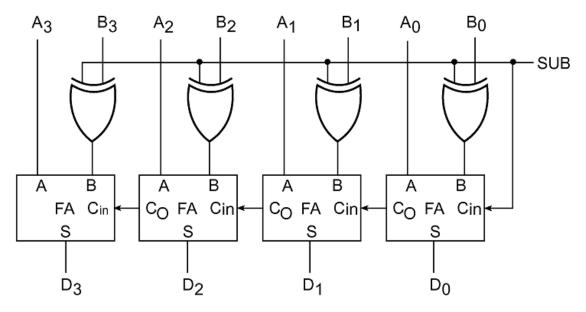

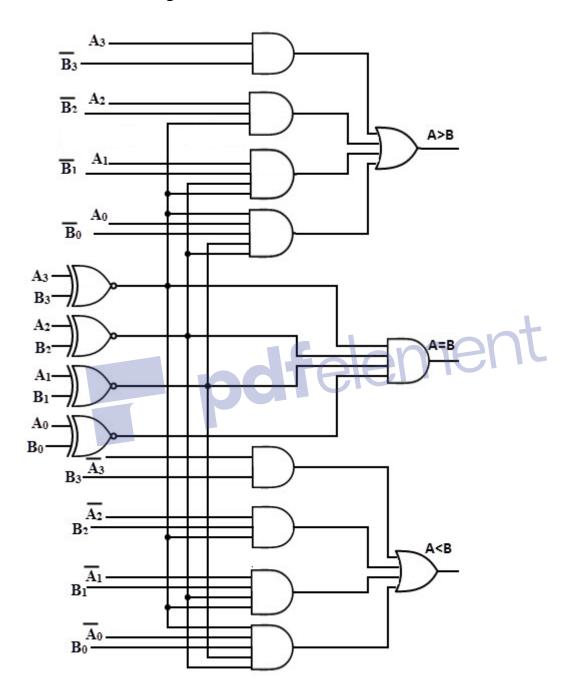

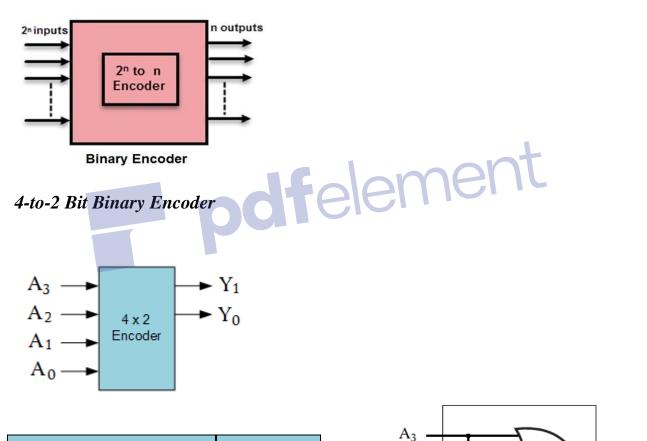

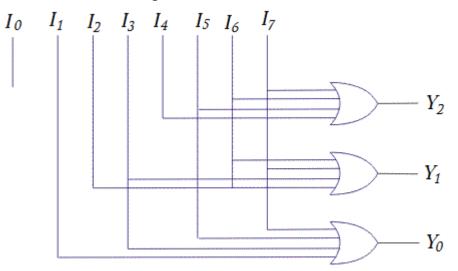

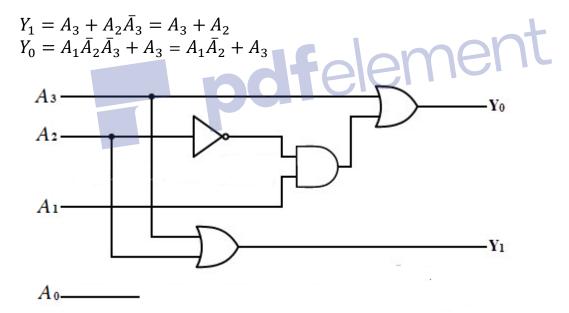

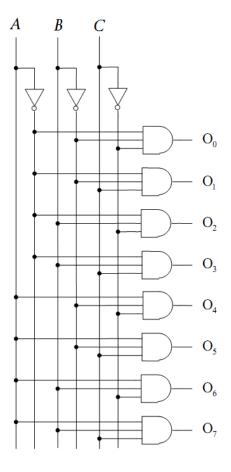

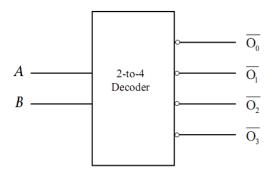

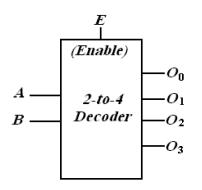

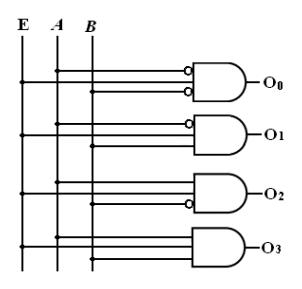

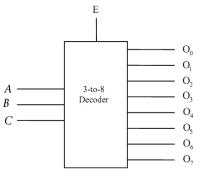

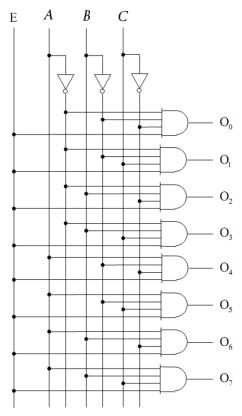

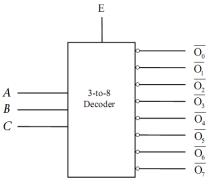

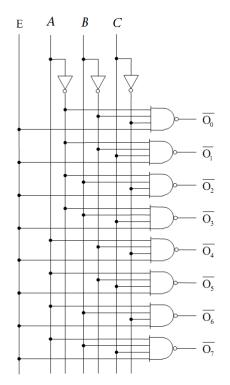

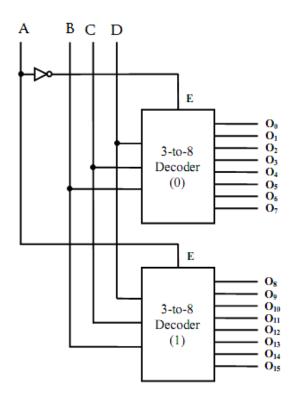

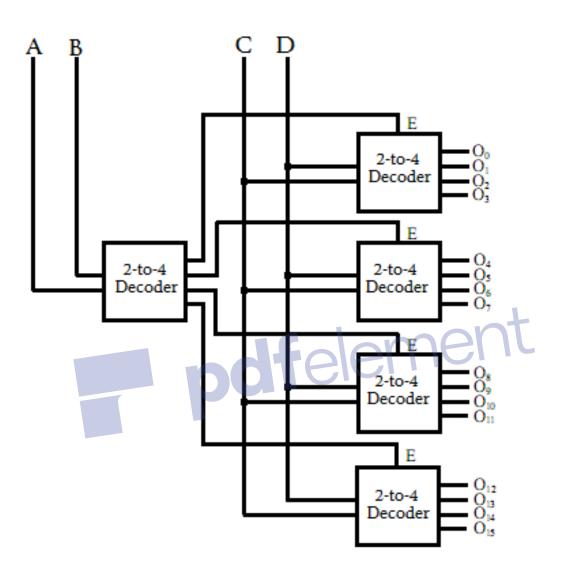

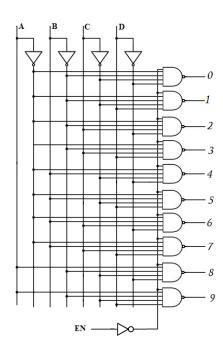

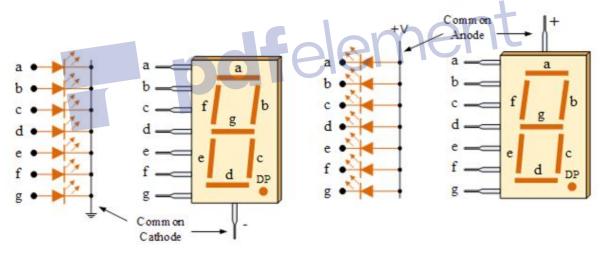

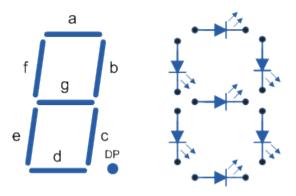

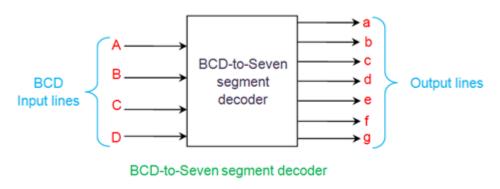

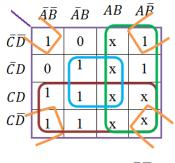

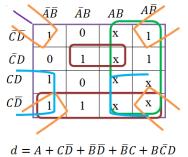

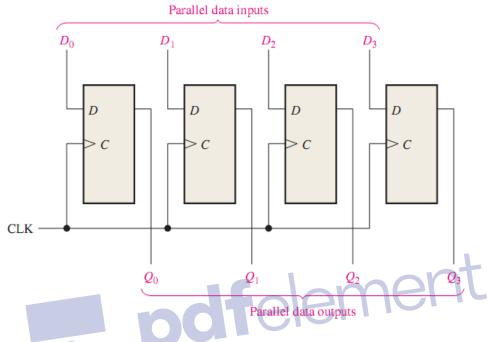

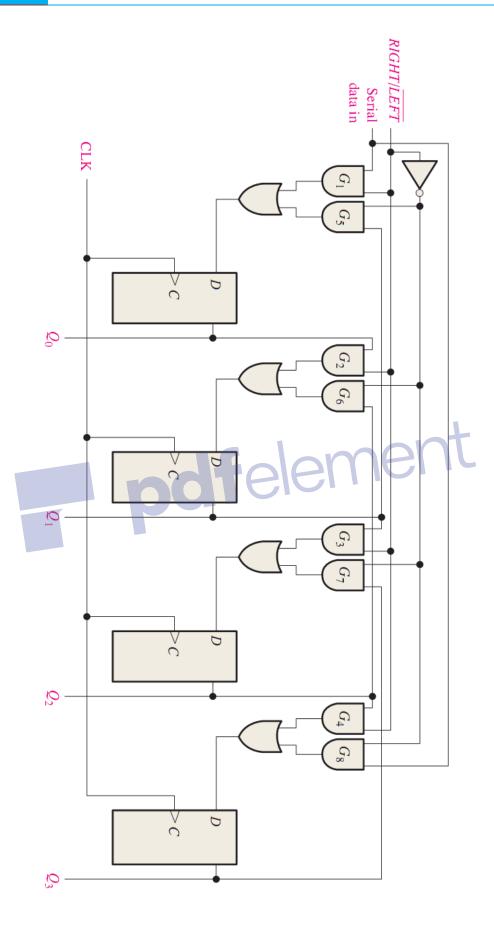

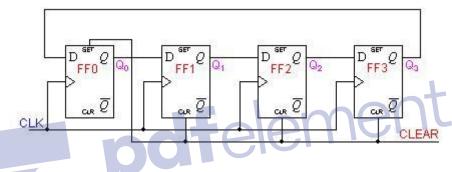

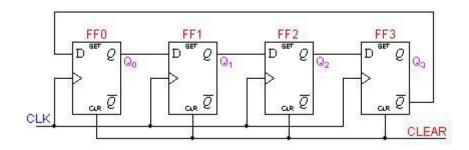

Simplify the following Boolean expression and show the minimum logic gate implementation.  $Y = \overline{B}(A + C) + C(\overline{A} + B) + AC$ Solution